- Есть вопросы?

- 8(961)1155384

- zakaz@kursach37.com

Электроника и микропроцессорная техника

Техническая реализация импульсных элементов ИИТ

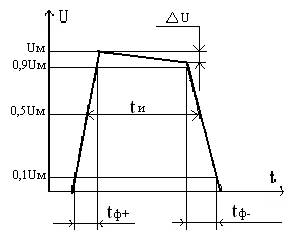

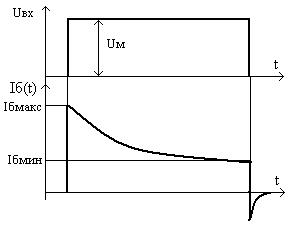

В общем смысле под импульсной техникой следует понимать совокупность методов расчёта и технических средств, позволяющую реализовать устройства логической обработки импульсных сигналов. Прямоугольным импульсным сигналом принято называть скачкообразное изменение токов и (или) напряжений, при этом эти параметры могут принимать только два значения: высокое и низкое (логические 0 или 1).В так называемой положительной логике высокому уровню соответствует логическая 1, низкому — логический 0, в отрицательной логике – наоборот.На рис.99 приведена временная диаграмма прямоугольного импульса с характеризующими его параметрами.

Рис.99

Параметры импульсного сигнала

Параметры импульсного сигнала

Uм — амплитуда импульса ,

g = DU/Uм — относительный завал

вершины импульса,

tи – длительность импульса,

tф+- передний фронт импульса,

tф- — задний фронт импульса.

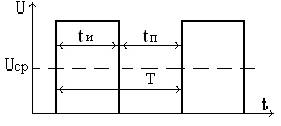

Длительности фронтов импульса представляют собой время, в течение которого напряжение импульса изменяется с 10% до 90% максимального значения –передний фронт, или с 90% до 10% — задний фронт. Последовательность импульсных сигналов представлена на рис.100 и , кроме параметров одиночного импульса, характеризуется рядом дополнительных характеристик таких как период (временной интервал между одинаковыми фазами двух соседних импульсов), скважность (отношение периода к длительности импульса), среднее напряжение (постоянная составляющая) импульсной последовательности, пауза (временной интервал между задним и передним фронтами двух соседних импульсов).

Рис.100 Импульсная последовательность tп — пауза

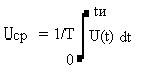

Скважность можно выразить как: Q=Т/tи = (tи + tп)/tи = 1 + tп/ tи ,при скважности равной двум (tи = tп) последовательность импульсов носит название «меандр». Среднее напряжение импульсной последовательности представляет собой:

, для U(t) = Uм = Const получим: Uср = Uм*tи/Т

Рассмотренный выше импульсный сигнал относится к классу видеоимпульсов, наиболее распространенному в импульсных устройствах ИИТ. Другие классы импульсных сигналов: радиоимпульсы, импульсы специальной формы здесь не рассматриваются. Основу построения логических устройств любой степени сложности составляют так называемые базовые логические элементы, выполняющие простейшие логические операции, они присутствуют практически во всех современных сериях цифровых интегральных схем. Так основой широко распространенной серии ИС транзисторно-транзисторной логики (ТТЛ-серии: К155 и усовершенствованные модификации К533, К555,К1533 и др.) является ключевой элемент (ключ) на биполярном транзисторе , выполняющий операцию логического отрицания. Используется также название ключа- инвертор.

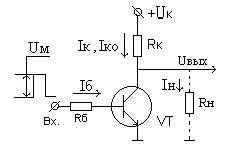

Схема транзисторного ключа приведена на рис.101. Характерной особенностью схемы является работа транзистора либо в режиме “закрыт”– рабочая точка на выходных характеристиках транзистора располагается на границе области отсечки (логический 0 по коллекторному току), либо в режиме “открыт” – рабочая точка располагается на границе области насыщения (логическая 1 по коллекторному току). Кроме того, из-за инерционных свойств транзистора переход рабочей точки из одного состояния в другое происходит не мгновенно, поэтому необходимо учитывать переходный процесс переключения, влияющий на параметры выходного импульса коллекторного тока.

Рис.101 Схема транзисторного ключа

Физически логические переменные Х и Y представлены уровнями напряжений входного и выходного сигналов соответственно. Условное графическое изображение инвертора показано на рис.102.

Рис.102 УГО инвертора

В состоянии насыщения транзистор как бы “стянут” в точку, грубой аналогией этого состояния может служить замкнутый механический тумблер. При этом в идеальном случае должно быть Uвых = 0 (логический 0 ),однако, реально Uвых равно напряжению насыщения транзистора (около 0,5В для Si – транзисторов), это напряжение называют остаточным параметром , характеризующим неидеальные свойства транзисторного ключа в указанном режиме. В режиме насыщения ток коллектора максимален , ограничен только сопротивлением коллекторной нагрузки Rк, обозначается символом Iк.н (ток коллектора насыщения) и равен:

Iк.н = (Uк – Uнас.)/Rк » Uк/Rк, поскольку Uнас.« Uк

Для поддержания коллекторного тока насыщения очевидно необходимо создать ток в базе транзистора теоретически величиной не менее:

Iб.н = Iк.н/h21Э – ток базы насыщения,h21Э- коэффициент передачи базового тока в коллектор для схемы с общим эмиттером.

Практически из – за технологического разброса h21Э, а также его нестабильности в температурном диапазоне реальный базовый ток должен быть больше теоретического значения, величина реального тока базы равна:

Iб.реал. = (Uм-Uбэ)/Rб » Uм/Rб, поскольку напряжение на открытом базо-эмиттерном переходе Uбэ«Uм.

Отношение: Iб.реал./ Iб.н = S называют коэффициентом насыщения (практически его величина лежит в пределах 5-10 относительных единиц).

В состоянии отсечки сопротивление между коллектором и эмиттером транзистора велико, грубой аналогией в этом случае является разомкнутый механический тумблер. При этом напряжение на выходе в идеальном случае должно быть равно напряжению коллекторного питания (если сопротивление нагрузки ключа бесконечно велико) и трактуется как логическая 1. Однако, из-за наличия теплового тока коллектора образуется напряжение на коллекторном резисторе и реальное напряжение на выходе будет равно:

Uвых= Uк – Iко*Rк (Rн = ?), т.е. несколько меньше (на единицы милливольт) идеального.

Напряжение Iко*Rк, также называется остаточным параметром в режиме отсечки и характеризует неидеальность ключа в этом режиме. Кроме того, указанный режим накладывает ограничения на предельную величину резистора, ограничивающего базовый ток.

Поскольку тепловой коллекторный ток создает напряжение на этом резисторе, причём его полярность является отпирающей для транзистора, то при слишком большой величине Rб транзистор из состояния отсечки может перейти в активный режим, т.е. произойдёт несанкционированное срабатывание ключа (низкий уровень напряжения логической 1 или вообще переход транзистора в открытое состояние). Опасность несанкционированного срабатывания резко возрастает, если ключ работает в широком температурном диапазоне, поскольку тепловой ток коллектора удваивается на каждые 10оС повышения температуры окружающей среды. Очевидно, что величина Rб должна быть ограничена сверху в соответствии с условием:

Rб ? Uбэ.пор./Iко.макс.,где Uбэ.пор.- напряжение отпирания транзистора по базе, Iко.макс.- максимальное значение теплового тока для данного типа транзистора и заданных условий внешней среды.

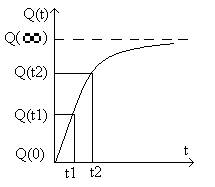

Переходный процесс переключения транзистора между указанными состояниями исследуется с помощью так называемого метода заряда в базе транзистора. Суть метода заключается в следующем — скорость изменения заряда в базе при переключениях ключа можно записать как:

dQ/dt = Iб – Q/t , где Q – заряд, Iб – установившееся значение тока базы, t -постоянная времени транзистора (пропорциональна времени жизни неосновных носителей заряда в базе), после очевидных преобразований получим:

t* dQ/dt +Q = Iб*t – неоднородное дифференциальное уравнение первого порядка, аналогичное уравнениям, описывающим поведение RC – цепей с одной реактивностью в переходном процессе, решение таких уравнений рассматривается в курсе теоретических основ электротехники и выглядит следующим образом:

Q(t) = Q(?) — [Q(?) – Q(0) ]*е-t/t ,

здесь Q(?) и Q(0)- граничные условия (установившиеся значения заряда через бесконечно большой промежуток времени и в начальный момент соответственно). Вид функции представлен на рис.103.

Рис.103. Экспоненциальная зависимость изменения заряда в базе при включении транзисторного ключа

Практический интерес представляет также интервал времени в течение которого заряд изменяется в определённых пределах, например для рис.103, в пределах от Q(t1) до Q(t2) из общего решения можно найти моменты времени t1, t2 и их разность:

Dt = t2 – t1 = t*ln{Q(?)-Q(t1)}/ {Q(?)-Q(t2)}

Временные диаграммы, поясняющие процесс переключения транзисторного ключа при подаче на его базу прямоугольного импульса тока и влияние переходного процесса на форму и параметры выходного (коллекторного) импульса тока приведены на рис.104.Обозначения на рис104:

- Qм =t*Iб — максимальный заряд {Q(?)},приобретаемый базой в течение входного импульса,

- Qн = t*Iбн — заряд базы, соответствующий току базы насыщения ,

- Iк.н – коллекторный ток насыщения.

Рис.104. Временная диаграмма переходного процесса в транзисторном ключе.

tзад. = t1-t0 –время заряда базо-коллекторной

ёмкости, приблизительно 0,25 t

tф+ = t2 –t1 — передний фронт коллектоного

импульса тока,

tрас. = t4 –t3- время рассасывания избыточного

заряда базы,

tф- = t5 – t4 –задний фронт коллекторного им-

пульса тока,

Dt = t3 – t2 – время накопления избыточного

заряда в базе (не влияющего на величину кол-

лекторного тока).

Пользуясь приведенными выше соотношениями, можно определить временные параметры импульса коллекторного тока, так для длительности переднего фронта получим:

Q(?) = Qм, Q(t1) = 0, Q(t2) = Qн — граничные условия рассматриваемой фазы импульса,

tф+ = t*ln{Q(м)-0}/ {Q(м)-Q(н)} = t*lnt*Iб/( t*Iб — t*Iбн) =t*ln 1/(1- Iбн/ Iб)= t*ln S/(S-1)

Применим разложение функции натурального логарифма в степенной ряд вида:

lnx »(x-1)/x +…, где х = S/(S-1), получим: tф+ » t/S

Из полученного выражения следует, что для уменьшения длительности переднего фронта необходимо увеличивать степень насыщения транзистора на этапе включения.

Таким образом, время включения транзистора при подаче отпирающего импульса тока в базу составит:

tвкл.= tзад.+ tф+= 0,25t+t/S

По изложенной методике найдем время рассасывания избыточного заряда в базе:

tрас. = t*ln {Q(t5) – Q(t3)}/ {Q(t5) – Q(t4)} = t*ln(0-t*Iб)/(0-t*Iбн)»t{1 – (1/S)}

В данном случае необходимо уменьшать насыщение транзистора, чтобы ускорить процесс его выключения , т.е. для улучшения параметров импульсов выходного коллекторного тока необходимо удовлетворить противоречивые требования относительно коэффициента насыщения транзистора.

Длительность заднего фронта выходного импульса найдем , предполагая, что его формирование закончилось при снижении величины заряда в базе до уровня 0,1Qн,тогда:

tф- = t*ln {Q(t5) – Q(t4)}/ {Q(t5) –0,1Q(t4)} = t*ln(0-t*Iбн)/(0-0,1t*Iбн) = 2,3t

Таким образом, время выключения транзистора составит: tвыкл. = tрас.+ tф-»t{3,3-(1/S)}.

Обычно время задержки срабатывания определяется как: tз.ср. = 0,5(tвкл.+tвыкл.)

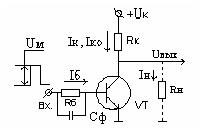

Известны методы ускорения переходных процессов транзисторного ключа, основные из них приведены ниже.

Метод форсирующего конденсатора основан на свойстве конденсатора сохранять неизменным напряжение на нём в момент поступления переднего фронта входного импульса, т.е. фактически в этот момент его реактивное сопротивление равно нулю (первый закон коммутации теории переходных процессов в RC-цепях). Схема включения форсирующего конденсатора приведена на рис.105.

Рис. 105. Включение форсирующего конденсатора Сф

Временные диаграммы, поясняющие принцип работы форсирующего конденсатора показаны на рис.106.

Рис.106. Ток базы ключа при наличии форсирующего конденсатора

В момент включения ток базы достигает максимальной величины –Iбмакс=Uм/Rбэ,где Rбэ- входное сопротивление транзистора, тем самым обеспечивается высокое значение коэффициента насыщения и минимальная длительность переднего фронта импульса коллекторного тока. По мере заряда конденсатора ток базы уменьшается и в конце входного импульса достигает минимальной величины Iбмин.=Uм/(Rб+Rбэ),обеспечивающей S=1.

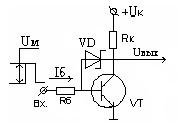

Метод введения нелинейной отрицательной обратной связи с использованием диода Шоттки также обеспечивает разное насыщение транзистора в процессе его коммутации аналогично предыдущему случаю, однако технологически проще реализуем в интегральном исполнении. Особенностью диода Шоттки является малый порог срабатывания и высокое быстродействие, благодаря чему отрицательная обратная связь срабатывает раньше чем транзистор ключа войдет в насыщение. Схема ключа с диодом Шоттки представлена на рис.107.

Рис. 107. Нелинейная обратная связь с диодом Шоттки

Падение напряжения на диоде Шоттки обеспечивает положительный потенциал коллектора относительно базы, предотвращая тем самым смещение коллекторно-базового перехода в прямом направлении и накопление избыточного заряда в базе. В современной схемотехнике ИС серии ТТЛ диод Шоттки интегрирован с транзистором (серии ИС ТТЛШ).

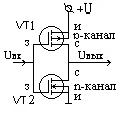

Инвертор (ключ) на полевых транзисторах является основой популярной серии ИС-КМОП (К561,564).Ключ выполнен на двух полевых транзисторах с дополнительной симметрией ( К- дополнительный),т.е. транзисторы имеют каналы различного типа проводимости. На рис.108 приведена схема такого ключа на полевых транзисторах с индуцируемыми каналами “p” и “n” типа.

Рис.108 Ключ на полевых транзисторах с дополнительной симметрией

Переключение ключа происходит , когда входное напряжение превышает по модулю порог срабатывания транзисторов. При этом Uпор.vт1 » -0,5U, Uпор.vт2 » +0,5U, таким образом при Uвх = 0 (логический ноль): VТ2 – закрыт, VТ1 – открыт, поскольку на его затворе действует потенциал равный минус U, на выходе формируется высокий уровень, примерно равный напряжению питания +U (логическая единица). При Uвх » +U (по входу ключ управляется выходным напряжением аналогичного элемента), состояние транзисторов противоположно предыдущему и на выходе напряжение оказывается близким к нулю (логический 0).Таким образом выполняется операция логического отрицания, в статическом состоянии ток потребления практически отсутствует, т.к.один из транзисторов всегда закрыт. При переключениях появляется входной ток, связанный с перезарядом подзатворных емкостей, величина этого тока тем больше, чем выше частота входного сигнала. Кроме того, наличие этих емкостей ограничивает частотный диапазон работы ключа и , следовательно, КМОП серии ИС, что сужает диапазон её применения.

На основе рассмотренных ключей строятся так называемые базовые элементы основных серий ИС: И-НЕ (штрих Шеффера), ИЛИ-НЕ (стрелка Пирса), на которых возможна реализация сложных логических устройств с наименьшими затратами аппаратных средств.

Базовый элемент И-НЕ серии ИС ТТЛ имеет условное графическое обозначение, показанное на рис.109 , выполняет логическую операцию ![]() , таблица истинности приведена ниже.

, таблица истинности приведена ниже.

![]()

Рис.109

Таблица истинности

УГО логической

операции

штрих Шеффера

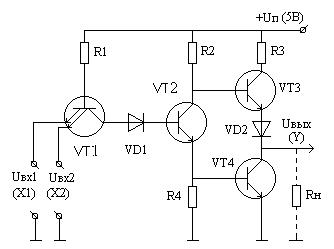

Принцип работы и техническая реализация указанного элемента показаны на рис.110. Основой схемы является многоэмиттерный транзистор VT1,выполняющий операцию конъюнкции (И), фактически он представляет собой интегрированный набор диодов по числу входов -2 и выходов -1.Операция НЕ реализуется транзисторами Vт2,Vт3,Vт4 с одновременным усилением выходного сигнала. Диоды VД1, VД2 необходимы для повышения порогов срабатывания транзисторов VТ2 и VТ3 с целью их надёжного запирания при низких уровнях входных напряжений. Резисторы R1 ?R4 обеспечивают допустимые режимы работы транзисторов по базовым и коллекторным токам транзисторов. Характерной особенностью ТТЛ схем является напряжение питание +5В.

Рис.110. Схема базового элемента И-НЕ ТТЛ

Введём обозначения физических уровней логических 1 и 0 как Е1 и Е0 соответственно.

Работа базового элемента происходит следующим образом:

Uвх1 = Uвх2 = Е0 –эмиттерные выводы VТ1 через внутренние сопротивления источников входных сигналов соединены с общей точкой , базо-эмиттерные переходы открыты и шунтируют коллекторно-базовый переход VТ1, ток базы VТ2 равен нулю и транзисторы VТ2 и VТ4 закрыты, в этом случае транзистор VТ3 отпирается током базы по цепи: Uп- R2- базо-эмиттерный переход VТ3- VД2-Rн-общая точка , на выходе формируется высокий уровень напряжения :

Е1 » Uп*Rн/(R3 + Rн) – логическая 1;

Uвх1 = Е1, Uвх2 = Е0 или Uвх1 = Е0, Uвх2 = Е1 – состояние схемы не изменяется, поскольку коллекторно – базовый переход VТ1 шунтирован обним из открытых базо-эмиттерных переходов, на выходе сохраняется логическая 1;

Uвх1 =Uвх2 = Е1 – оба базо-эмиттерных перехода VТ1 закрыты высокими запирающими напряжениями, открывается коллекторно-базовый переход транзистора VТ1 и его коллекторный ток открывает транзистор VТ2 по цепи: Uп- R1-коллекторно-базовый переход VТ1-VД1-база VТ2, эмиттерный ток VТ2 создаёт напряжение на резисторе R4, отпирающее транзистор VТ4, тем самым вывод выхода оказывается соединённым с общей точкой через малое сопротивление между коллектором и эмиттером открытого VТ4 и на выходе формируется низкое напряжение Е0 (логический ноль).

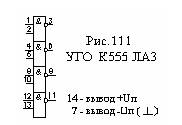

Таким образом, приведенная схема реализует таблицу истинности логической операции штрих Шеффера. Типичным представителем рассмотренного базового логического элемента является микросхема серии ТТЛ — К555ЛА3, содержащая 4 двухвходовых элемента И-НЕ, УГО этой микросхемы приведено на рис.111.

Основные параметры и характеристики базового логического элемента ТТЛ:

- I1вх » 40 мкА – входной ток при Uвх = Е1 (обратный ток базо-эмиттерного перехода VТ1),

- I0вх » 1,6 мА — входной ток при Uвх = Е0 (максимальное значение для открытого базо-эмиттерного перехода VТ1),

- I1вых = I0 вых » 16 мА –максимально допустимый выходной ток,

- коэффициент разветвления: n = Iвых/I0вх = 16 – допустимое количество аналогичных логических элементов, которое может быть подключено к выходу одного базового логического элемента при создании сложных логических устройств,

- Uвых = Е1 » 2.4 …4,5В в зависимости от величины сопротивления нагрузки,

- Uвых = Е0 » 0,2…0,4В в зависимости от величины выходного тока ,

- Uвх = Е1 или Е0 поскольку логические элементы одной серии ИС как правило соединены по выходам / входам между собой,

- быстродействие базового логического элемента оценивается временем перехода выходного напряжения из состояния Е0 в Е1 (t01) или наоборот (t10) и зависит от задержки срабатывания транзисторных ключей, рассмотренной ранее. Обычно принимают t01=t10 »3 tз.ср., практически эта величина находится в пределах 10…20 наносекунд,

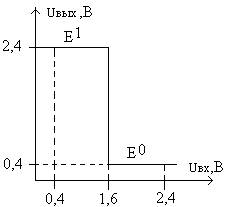

- помехоустойчивость ИС ТТЛ можно оценить по передаточной характеристике, идеализированный вид которой для наиболее тяжелого режима (минимально допустимое сопротивление нагрузки), приведен на рис.112.

Рис.112. Передаточная характеристика базового ТТЛ — элемента

1,6 В – пороговое напряжение

срабатывания

Для состояния Uвх = Е0 и Uвых = Е1 возможно ложное срабатывание элемента, если напряжение помехи относительно шины «земля» будет равно: Uпом.зем. ? 1,6 – 0,4 = 1,2В.

Для состояния Uвх = Е1 и Uвых = Е0 ложное срабатывание возможно, если напряжение помехи относительно шины «питание» по модулю будет равно Uпом.пит.? 2,4 – 1,6 = 0,8В.Практически с учетом влияния температуры внешней среды считается допустимой помеха не более 0,6В.

потребляемая базовым логическим элементом мощность относительно велика и составляет около 20 мВТ.

Следует отметить, что элементы ТТЛ чувствительны к величине внутреннего сопротивления источника входного сигнала (Ri), действительно, если Ri ? 1Ком,то в состоянии Uвх = Е0 падение напряжения на нём от входного тока может превысить пороговое напряжение, что приведёт к несанкционированному срабатыванию.

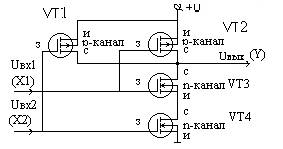

Базовый логический элемент И – НЕ серии ИС КМОП.

Основой указанной серии ИС является рассмотренный ранее ключ на полевых транзисторах с дополнительной симметрией , УГО, логическое уравнение, таблица истинности аналогичны приведенным для элемента И-НЕ ТТЛ.

Напряжение питания ИС этой серии отличается широким диапазоном 3…15В, потребляемая мощность в статическом режиме не превышает 0,1мВт, входное сопротивление весьма велико (> 1 Мом), благодаря этому КМОП ИС находят широкое применение в схемотехнике в случаях, когда не предъявляются повышенные требования к быстродействию. Быстродействие КМОП логического элемента находится в пределах 100 – 200 наносекунд и определяется свойствами ключевого элемента, рассмотренными выше. Принцип работы базового элемента поясняется схемой приведенной на рис.113.

Рис.113. Логический элемент КМОП штрих Шеффера

Работа базового элемента происходит следующим образом:

- Uвх1 =Uвх2 = Е0 – затворы всех транзисторов через внутренние сопротивления источников входных сигналов соединены с общей точкой , низкий уровень входных сигналов является запирающим для транзисторов с n-каналом (VТ3, VТ4) и отпирающим для транзисторов с p-каналом (VТ1, VТ2), на выходе формируется высокий уровень напряжения Е1 по цепи: +U – параллельно соединённые проводящие каналы транзисторов VТ1 и VТ2 – Uвых, от общей точки вывод выходного напряжения отключён запертыми каналами транзисторов VТ3, VТ4,

- Uвх1 = Е1, Uвх2 = Е0 – по выходу состояние схемы не изменяется, поскольку высокое напряжение +U подключено к выходному выводу через проводящий канал транзистора VТ1 , при этом каналы VТ2 и VТ4 — заперты , т.к. напряжения на их затворах Е1 и Е0 соответственно , не превышают порогов срабатывания, открытый канал транзистора VТ3 не имеет значения в связи с тем , что последовательно с ним включен запертый канал VТ4, прерывающий гальваническую связь выходного вывода с общей точкой,

- Uвх1 = Е0, Uвх2 = Е1 — Uвых по прежнему равно Е1, поскольку закрыты каналы транзисторов VТ1 и VТ3 и открыты каналы транзисторов VТ2 и VТ4 ,

- Uвх1 = Uвх2 = Е1 – закрыты каналы транзисторов VТ1 и VТ2, открыты каналы транзисторов VТ3 и VТ4, таким образом, прервана гальваническая связь выходного вывода с выводом +U и он подключен к общей точке через открытые каналы транзисторов VТ3 и VТ4.

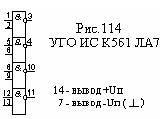

Базовый элемент ИС КМОП серии обладает высокой помехоустойчивостью: Uпом.пит» Uпом.зем » 0,5Uпит. В связи с высокими входными сопротивлениями коэффициент разветвления «n» может достигать 100 единиц. Типичным примером выпускаемых ИС рассмотренного типа может служить микросхема, показанная на рис.114.

Базовый логический элемент ИС серии ЭСЛ (эмиттерно- связанная логика) .

Отличительными особенностями указанной серии являются:

- в состоянии «включено» транзисторы работают без насыщения (без накопления избыточного заряда в базе),

- с целью повышения помехоустойчивости к общей точке схемы подключен положительный полюс источника питания , поэтому входные и выходные напряжения имеют отрицательную полярность,

- наличие двух выходов – прямого и инверсного.

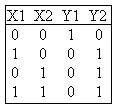

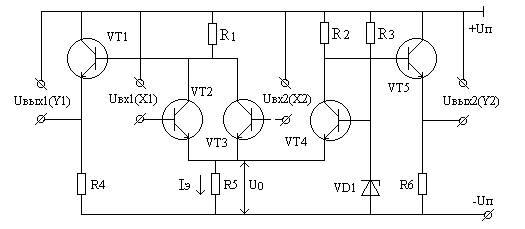

Приведенная на рис.115 схема базового логического элемента (БЛЭ) этой серии ИС выполняет две логические операции:

![]()

Таблица истинности выглядит следующим образом:

Рис.115. Базовый элемент ЭСЛ 2 ИЛИ, 2ИЛИ-НЕ

Транзисторы VТ1 и VТ5 работают в режиме эмиттерных повторителей, обеспечивая усиление выходных сигналов по мощности. Транзисторы VТ2, VТ3 являются входными, на их базы подаются напряжения соответствующие логическим уровням Е1 и Е0 ,измеряемые относительно общей точки и, следовательно, имеющие отрицательную полярность. Транзистор VТ4 является опорным, задающим режим переключения входных транзисторов , потенциал его базы (Uо) фиксируется постоянным относительно шины +Uп в данном случае с помощью стабилитрона VD1 (возможны и другие способы). Эмиттеры входных и опорного транзисторов связаны между собой (отсюда название ЭСЛ) и подключены к общему резистору отрицательной обратной связи по эмиттерному току R5. Все транзисторы имеют одинаковые параметры, поскольку изготавливаются в едином технологическом процессе. Резисторы R1, R2 являются коллекторными нагрузками, резистор R3 – задаёт режим работы стабилитрона по току, резисторы R4, R6 – нагрузки эмиттерных повторителей.

Принцип работы БЛЭ основан на переключении эмиттерного тока опорного транзистора на один или оба входных транзистора в зависимости от комбинации входных сигналов, в последнем случае ток опорного транзистора распределяется пополам между входными транзисторами в силу симметрии схемы.

Рассмотрим работу элемента при комбинациях входных и выходных сигналов в соответствии с таблицей истинности. Согласно первой строке таблицы оба входных сигнала имеют низкий логический уровень, т.е. Uвх1 = Uвх2 = Е0 — транзисторы VT2,VT3 закрыты, т.к. потенциалы их баз относительно шины –Uп меньше напряжения отрицательной обратной связи Uо на величину DUбэ. Это объясняется тем, что логические элементы одной серии соединены друг с другом и для рассматриваемой комбинации входных сигналов можно считать, что на базы VT2,VT3 поступает напряжение с выхода другого БЛЭ, находящегося в состоянии логического нуля, т.е. в данном случае аналогичное существующему на резисторе R6 . Опорный транзистор VT4 открыт, режим его работы близок к эмиттерному повторителю, поскольку схемотехнически реализовано соотношение R2 « R5 и опорное напряжение (Uо) практически полностью повторяется на резисторе ООС R5. Поскольку VT4 открыт, то потенциалы его коллектора и базы VТ5 находятся на низком уровне относительно шины –Uп . Следовательно , на резисторе R6 напряжение относительно шины –Uп также мало, т.е. меньше Uо: DUбэ = Uо – UR6. Тогда выходное напряжение, измеряемое относительно общей точки (+Uп), равное падению напряжения между коллектором и эмиттером VТ5, будет высоким по модулю: |Uвых2| = |Uп| — | UR6| и низким с учётом его знака (»-1,5В), этому значению в серии ИС ЭСЛ соответствует логический ноль Y2 = 0 (прямой выход БЛЭ). В свою очередь, высокий относительно шины –Uп потенциал объединённых коллекторов закрытых VT2,VT3 будет повторяться на эмиттерной нагрузке VТ1 – резисторе R4 и, следовательно, Uвых1 будет мало по модулю и велико с учетом знака (»-0,9В), т.е. соответствовать логической 1: Y1 = 1 (инверсный выход).

Для комбинаций входных сигналов: Uвх1 =Е1, Uвх2 = Е0 ; Uвх1 =Е0, Uвх2 = Е1 ;

Uвх1 =Е1, Uвх2 = Е1, реализующих 2ю, 3ю и 4ю строки таблицы истинности соответственно, происходит , как указывалось выше, переключение тока опорного транзистора на открытый входной транзистор. Например, для комбинации Uвх1 =Е1, Uвх2 = Е0 открыт транзистор VТ2 высоким уровнем напряжения относительно шины –Uп , поступающим с аналога резистора R4 предыдущего элемента , находящегося в состоянии Y1 = 1.Схемотехникой обеспечивается соотношение: Uвх1 = Uо + DUбэ, это напряжение практически полностью повторяется на резисторе обратной связи R5, в результате напряжение на базе опорного транзистора становится отрицательным и он закрывается: DUбэ.VT4 = Uо – Uо- DUбэ = -DUбэ.

Таким образом, ток опорного транзистора переключается на входной транзистор VT2, потенциал коллектора VT2 ( и базы VT1) относительно шины –Uп уменьшается, низкий потенциал базы VT1 практически без изменения повторяется на резисторе R5.

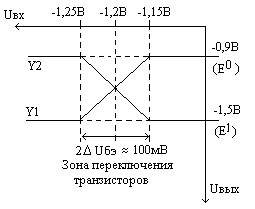

Таким образом, на выходе VT1 формируется высокое по модулю и низкое с учетом знака напряжение Uвых1» -1,5В, трактуемое как логический ноль (Е0) на инверсном выходе, аналогичным образом легко убедиться, что на прямом выходе Uвых2 » -0,9В, т.е.логическая единица (Е1). Процессы, протекающие в схеме для остальных комбинаций входных сигналов принципиально не отличаются от рассмотренного выше ( в последней комбинации ток опорного транзистора переключается на оба входных транзистора и делится между ними пополам). Следует отметить, что из-за высоких усилительных свойств транзисторов напряжение их переключения весьма мало: DUбэ » 50мВ, кроме того очевидно, что должно выполняться соотношение: Uо = (Е1 +Е0)/2 = -(0,9 +1,5)/2 = -1,2В. Процесс переключения поясняется передаточными характеристиками приведенными на рис.116 для прямого и инверсного выходов.

Рис.116 Передаточная характеристика базового логического элемента ЭСЛ

2 ИЛИ, 2ИЛИ-НЕ

Достоинством ИС серии ЭСЛ является высокое быстродействие – tз.ср. ? 1…2нС, обусловленное тем, что транзисторы в открытом состоянии работают без насыщения из-за глубокой отрицательной обратной связи и малой величины отпирающего напряжения, благодаря чему время рассасывания заряда базы мало и , следовательно, мало время выключения входных транзисторов. Время включения также мало из-за регенеративного режима переключения, связанного с ОС и малого времени перезаряда входных емкостей транзисторов через относительно малые сопротивления резисторов (R1 = R2 = 200…300 Ом). К недостаткам ИС ЭСЛ относятся: высокая потребляемая мощность, связанная с работой эмиттерных повторителей в активном режиме (? 50мВт) и невысокая помехоустойчивость из – за малых уровней переключающих напряжений. По указанным причинам серия ИС ЭСЛ имеет ограниченное применение.

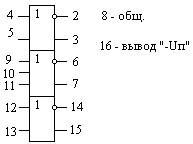

К ЭСЛ сериям ИС относятся К1500, К1590, в качестве практического примера на рис.117 приведено условное графическое изображение элемента К1590 ЛМ105.

Рис.117 Базовый элемент ЭСЛ К1590ЛМ105

2(2ИЛИ, 2ИЛИ – НЕ), 3ИЛИ, 3ИЛИ — НЕ

Таблица сравнительных параметров базовых элементов

| Тип серии ИС |

Е0 (В) |

Е1 |

Рпотр. |

tз.ср. |

Коэфф. разветвл. n |

Uпомех. |

Uп. |

|

ТТЛ |

0,2 – 0,4 |

2,4 — 4 |

? 20 |

5…20 |

?10 |

0,8…1,1 |

+5 |

|

КМОП |

0,2 – 0,4 |

»0,9Uп. |

?0,1 |

?200 |

до 200 |

»0,5Uп. |

+ 3…15 |

|

ЭСЛ |

— 1,5 |

— 0,9 |

20…50 |

1…3 |

?10 |

? 0,3 |

— 5 |